28

9152BINDCO02/10

ATA8743

12.7 Instruction Execution Timing

This section describes the general access timing concepts for instruction execution. The AVR

CPU is driven by the CPU clock clk

CPU

, directly generated from the selected clock source for the

chip. No internal clock division is used.

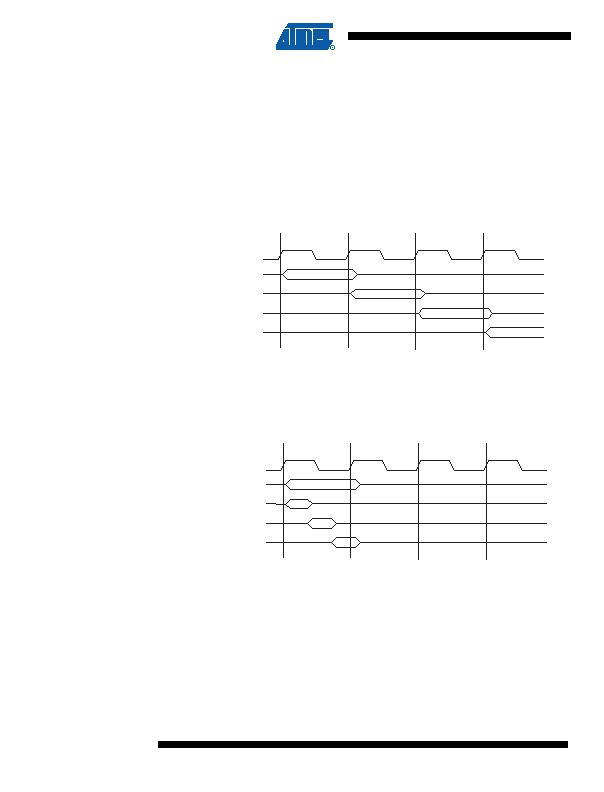

Figure 12-4 on page 28 shows the parallel instruction fetches and instruction executions

enabled by the Harvard architecture and the fast access Register File concept. This is the basic

pipelining concept to obtain up to 1 MIPS per MHz with the corresponding unique results for

functions per cost, functions per clocks, and functions per power-unit.

Figure 12-4. The Parallel Instruction Fetches and Instruction Executions

Figure 12-5 on page 28 shows the internal timing concept for the Register File. In a single clock

cycle an ALU operation using two register operands is executed, and the result is stored back to

the destination register.

Figure 12-5. Single Cycle ALU Operation

12.8 Reset and Interrupt Handling

The AVR provides several different interrupt sources. These interrupts and the separate Reset

Vector each have a separate Program Vector in the Program memory space. All interrupts are

assigned individual enable bits which must be written logic one together with the Global Interrupt

Enable bit in the Status Register in order to enable the interrupt.

The lowest addresses in the Program memory space are by default defined as the Reset and

Interrupt Vectors. The complete list of vectors is shown in

Interrupts

on page 66. The list also

determines the priority levels of the different interrupts. The lower the address the higher is the

priority level. RESET has the highest priority, and next is INT0 the External Interrupt Request

0.

clk

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

nd Instruction Execute

3rd Instruction Fetch

rd Instruction Execute

4th Instruction Fetch

T1

T2

T3

T4

CPU

Total Execution Time

egister Operands Fetch

ALU Operation Execute

Result Write Back

T1

T2

T3

T4

clk

CPU

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ATAVRRZ200

KIT DEMO AT86RF230

AV101-12LF

ATTENUATOR HIP3 0.70-1GHZ 8-SOIC

AV102-12LF

ATTENUATOR HIP3 1.7-2GHZ 8SOIC

AV113-12LF

ATTENUATOR HIP3 2.1-2.3GHZ 8SOIC

AXUV100G

SENSOR ELECTRON DETECTION

B0205F50200AHF

XFRMR BALUN RF 200-500MHZ 1608

B0310J50100AHF

XFRMR BALUN RF 300-1000MHZ 0805

B0322J5050AHF

XFRMR BALUN RF 300-2200MHZ 0805

相关代理商/技术参数

ATAB5275

功能描述:射频开发工具 LF Tx Antenna driver board (TPMS) RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V

ATAB5276

功能描述:射频开发工具 1A Antenna Driver Demoboard RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V

ATAB5278

功能描述:射频开发工具 LF Tx Antenna driver board (PEG) RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V

ATAB5279

功能描述:射频开发工具 LF Transmitter with ATA5279 RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V

ATAB5282

功能描述:BOARD EVAL LF 125KHZ ANT DVR 3CH RoHS:是 类别:RF/IF 和 RFID >> RFID 评估和开发套件及电路板 系列:Smart RF 产品培训模块:M24LR64 Dual Interface EEPROM 标准包装:1 系列:- 类型:读取器模块 频率:13.56MHz 适用于相关产品:M24LR-64-R 已供物品:2 根基准天线,I2C 和 RFID 读取器,样品 其它名称:497-10480

ATAB5283

功能描述:射频开发工具 LF Rx Board 1 channel (TPMS)

RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V

ATAB5423-3-B

功能描述:射频开发工具 UHF Transceiver Base station Board 315MHz

RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V

ATAB5423-3-WB

功能描述:射频开发工具 UHF TRx Application Board 315MHz RoHS:否 制造商:Taiyo Yuden 产品:Wireless Modules 类型:Wireless Audio 工具用于评估:WYSAAVDX7 频率: 工作电源电压:3.4 V to 5.5 V